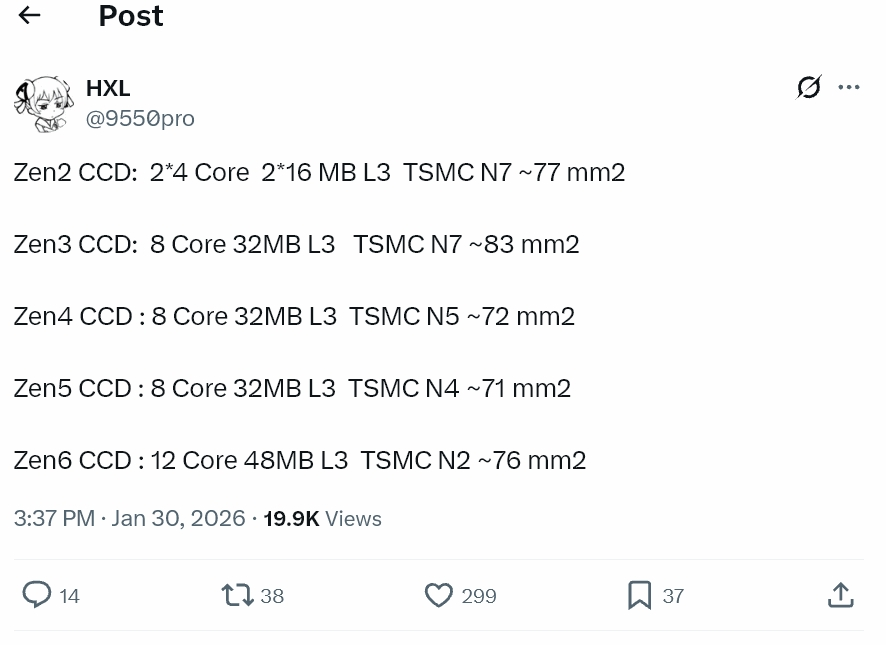

Neue Gerüchte deuten darauf hin, dass AMD mit Zen 6 einen deutlichen Schritt bei seinen CPU-Chiplets plant. Demnach könnten die sogenannten CCDs künftig 12 statt 8 Kerne enthalten – ein Plus von 50 Prozent pro Chiplet.

Zusätzlich sollen alle 12 Kerne in einem einzigen CCX zusammengefasst sein und sich einen 48 MB großen L3-Cache teilen. Das würde nicht nur den Cache vergrößern, sondern auch die interne Struktur vereinfachen, was vor allem bei latenzsensitiven Anwendungen Vorteile bringen könnte.

Möglich wird dieser Ausbau vermutlich durch den Wechsel auf TSMCs 2-nm-Fertigungsprozess (N2). Trotz mehr Kernen und größerem Cache soll die Chipfläche nur leicht wachsen, was für eine deutlich höhere Transistordichte spricht.

Auch 3D V-Cache bleibt laut Leak ein zentrales Thema: Künftige X3D-Modelle könnten bis zu 144 MB L3 pro CCD bieten – auf Desktop-CPUs mit zwei CCDs wären damit sogar bis zu 288 MB Gesamt-Cache möglich.

Offiziell bestätigt ist das alles noch nicht. Sollte sich das Gerücht jedoch bewahrheiten, wäre Zen 6 kein kleines Update, sondern ein grundlegender Schritt nach vorn bei AMDs Chiplet-Design.

*Quelle: HXL (Twitter)