AMD plant Berichten zufolge, zwischen 2025 und 2026 Glassubstrate in seine Hochleistungssystem-in-Packages (SiPs) einzubauen. Glassubstrate bieten mehrere Vorteile gegenüber herkömmlichen…

Durchsuche: Chiplet

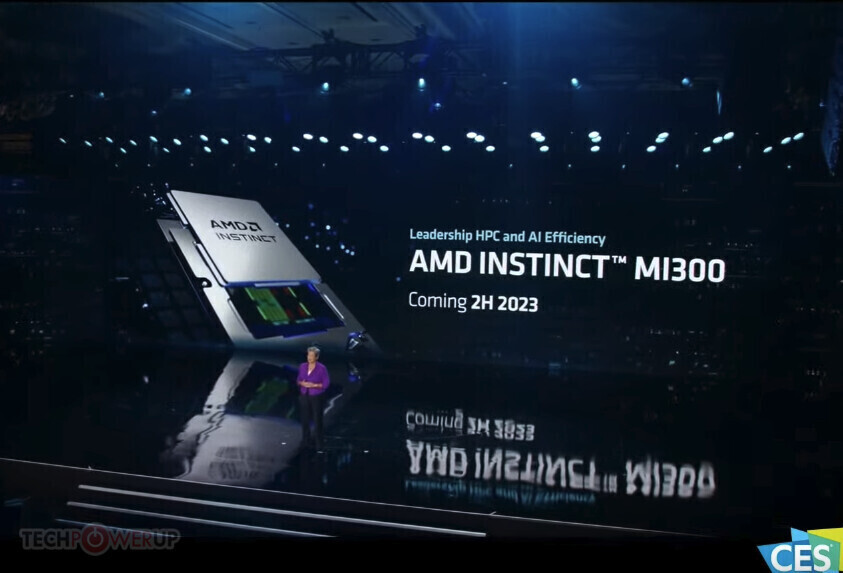

Während der CES 2023 Keynote kündigte AMD seine neueste Instinct MI300 APU an, ein Novum in der Welt der Rechenzentren.…

AMD bringt Berichten zufolge die Markenerweiterung „XTX“ zurück zu den Haupt-Marketing-Namen seiner kommenden Radeon RX 7000-Serien SKUs. Bisher hatte das…

Le Comptoir du Hardware hat einen Die-Shot einer 2P+8E-Core-Variante der „Meteor Lake“-CPU geknipst, worauf hin ein Interessanter Kommentar hinterlassen wurde.…

Intels kommende „Meteor Lake“ und „Arrow Lake“ Client-Mobilprozessoren führen eine interessante Wendung des Chiplet-Konzepts ein. Früher in vage aussehenden IP-Blöcken…

AMD hat bereits bekannt gegeben, dass die CPU-Kernzahl seiner EPYC-Prozessoren „Genua“ und „Bergamo“ 96 bzw. 128 betragen wird. Diese Kernzahl…

AMD hat am 1. April einen neuen Patentantrag veröffentlicht, der zu zeigen scheint, in welche Richtung sich das Chiplet-GPU-Design entwickelt.…

AMD hat ein Patent eingereicht, in dem sie ein MLA-Chiplet-Design beschreiben, das mit einer GPU-Einheit und einer Cache-Einheit gepaart werden…

Laut Angaben von DigiTimes, wird TSMC im März 2020 mit der Massenproduktion seiner 5-nm-Nodes beginnen. Damit Unternehmen, die das 5-nm-PDK…