Rambus Inc. (NASDAQ: RMBS), ein führender Anbieter von Chips und Silizium-IP, der Daten schneller und sicherer macht, gab heute die…

Durchsuche: Silizium

AMD bringt Berichten zufolge die Markenerweiterung „XTX“ zurück zu den Haupt-Marketing-Namen seiner kommenden Radeon RX 7000-Serien SKUs. Bisher hatte das…

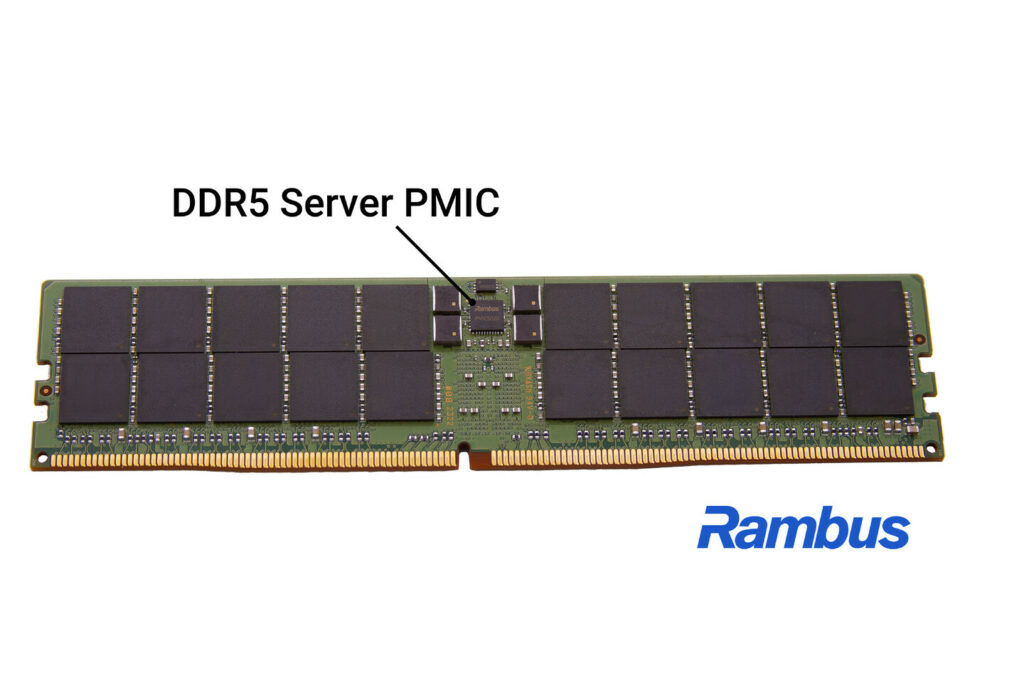

Rambus Inc., ein führender Anbieter von Chips und Silizium-IP-Technologie, die Daten schneller und sicherer macht, gab heute die Verfügbarkeit seines…

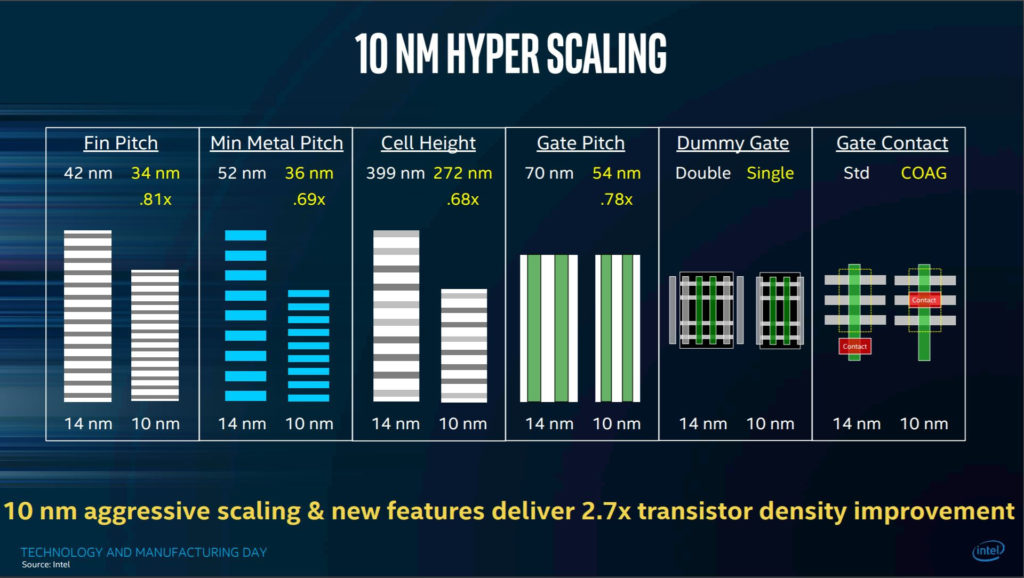

Intel wird, laut diverser Angaben, zum dritten mal die Auslieferung der ersten Prozessoren im 10 Nanometer Silizium Herstellungsprozess verschieben. Die…