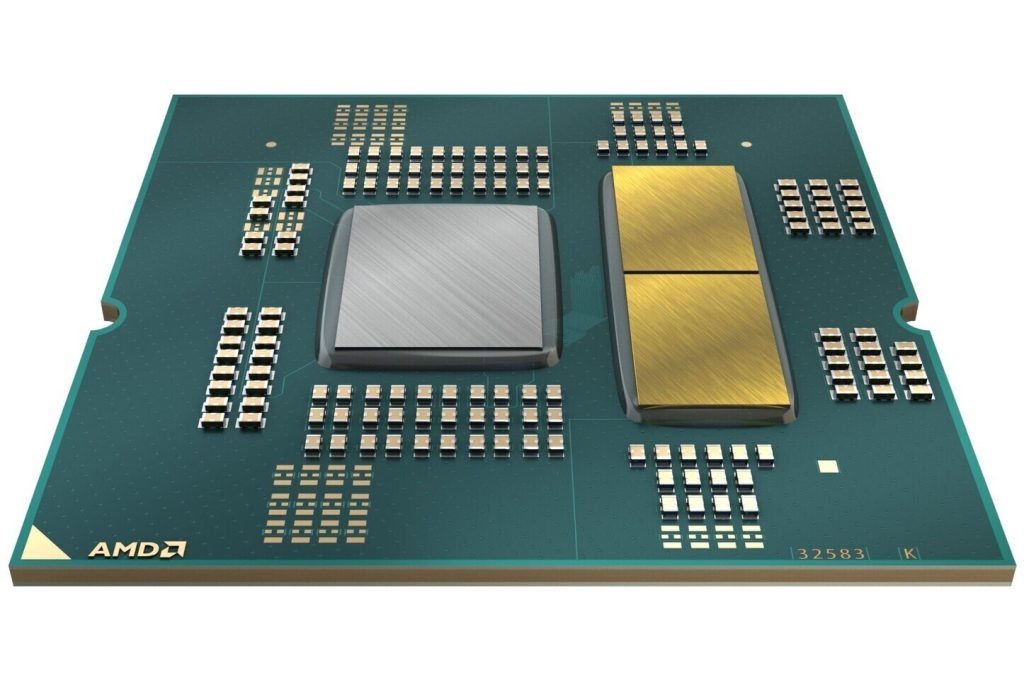

AMD setzt bei „Zen 6“ auf eine Split-Node-Strategie: Die CPU-Core-Chiplets entstehen im 2-nm-Prozess (N2P), während die I/O-Dies im günstigeren 3-nm-Prozess (N3P) gefertigt werden. Erste Auslieferungen werden ab Ende Q3 2026 erwartet.

Jedes CCD soll bis zu 12 Kerne mit SMT sowie rund 48 MB L3-Cache enthalten. Desktop-Modelle kombinieren bis zu zwei CCDs mit einem IOD, also maximal 24 Kerne und 48 Threads. EPYC-Servervarianten („Venice“) skalieren weiter und führen PCIe Gen 6 sowie bis zu 1,6 TB/s Speicherbandbreite ein.

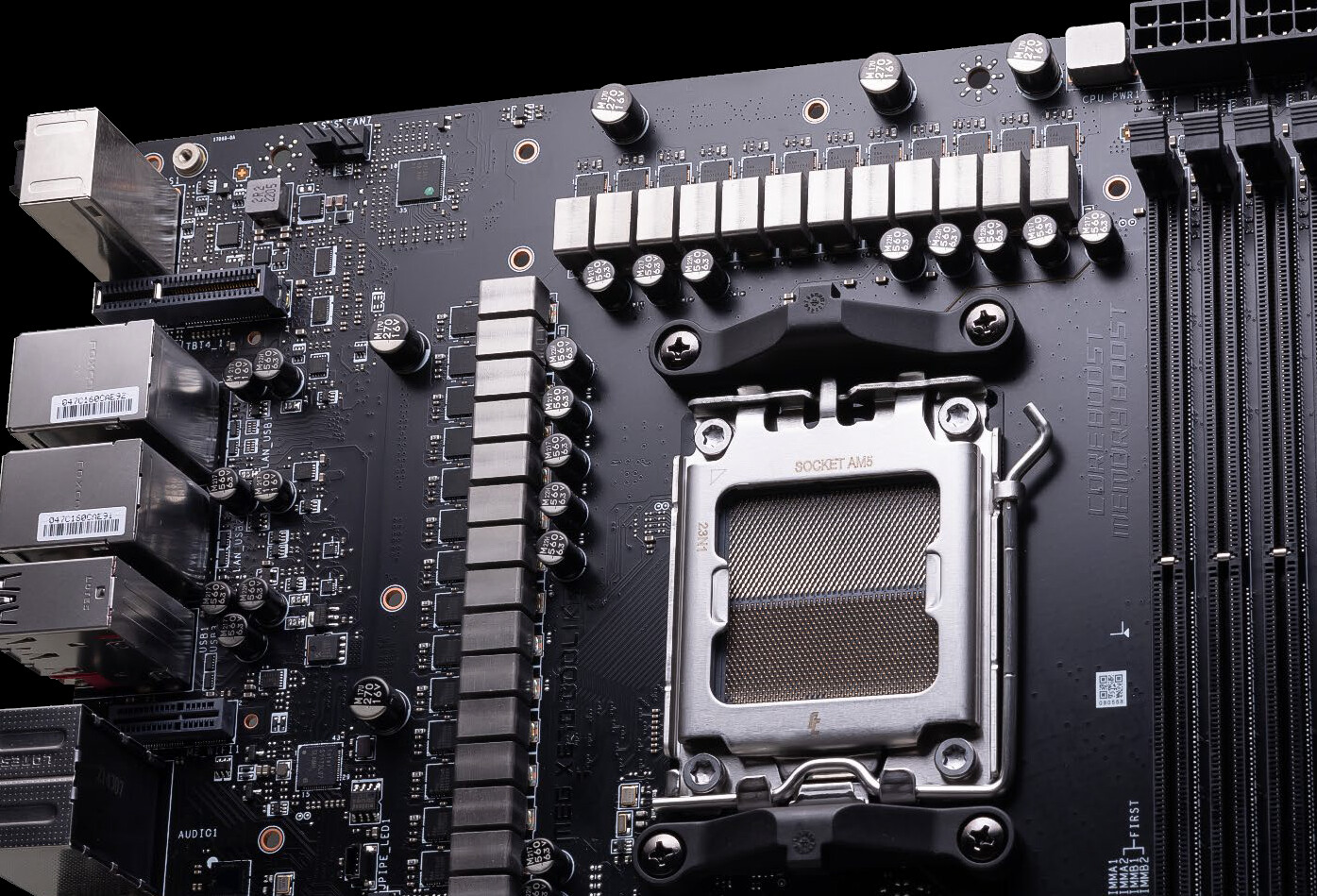

Erwartet werden zweistellige IPC-Zuwächse, höhere Taktraten und bessere Effizienz. Der AM5-Sockel bleibt erhalten, sodass Aufrüstungen ohne Plattformwechsel möglich sind.

*Quelle und Bild: Techpowerup